DOI:10.16136/j.joel.2022.05.0630

## 自适应光电混合互连分流结构建模与性能分析

惠 超1,蒋 林2\*,山 蕊1,杨博文1,罗佳莹1,冯 煜1

(1. 西安邮电大学 电子工程学院,陕西 西安 710121; 2. 西安科技大学 集成电路实验室,陕西 西安 710054)

摘要:针对片上光电混合互连网络(hybrid optoelectronic network-on-chip, HONoC)拥塞控制与自适应能力差、无法实现光电联合仿真等问题,提出一种适用于可重构阵列处理器的自适应光电混合互连分流结构,在此结构上设计了自适应分流路由算法与一种低损耗无阻塞的5端口光路由器,并搭建了基于 System verilog与 Verilog的光电混合互连功能仿真与性能统计模型。实验结果表明,在边缘节点阻塞的情况下所设计的路由算法避免拥塞能力平均提升了17.5%,光路由器所需交叉波导与微环谐振器数量大幅减少,平均光路由器级插入损耗仅为0.522 dB,所设计的光电混合互连性能统计模型具有支持设计拓扑、结构和路由策略等功能,并且可以对资源使用、功耗开销、插入损耗等性能进行统计分析。

关键词:片上光电混合互连;电配置路由器;分流结构;光路由器;性能分析中图分类号:TN919.21 文献标识码:A 文章编号:1005-0086(2022)05-0521-08

# Modeling and performance analysis of adaptive optoelectronic hybrid interconnection shunt structure

HUI Chao¹, JIANG Lin²\*, SHAN Rui¹, YANG Bowen¹, LUO Jiaying¹, FENG Yu¹ (1, College of Electronic Engineering, Xi′an University of Posts & Telecommunications, Xi′an ,Shaanxi 710121, China; 2, Laboratory of Integrated Circuit, Xi′an University of Science and Technology, Xi′an, Shaanxi 710054, China)

**Abstract**: Aiming at the problems of hybrid optoelectronic network-on-chip (HONoC), such as congestion control and poor adaptive capabilities, and the inability to realize optoelectronic co-simulation, an adaptive hybrid optoelectronic interconnection shunt structure suitable for reconfigurable array processors is proposed. Based on this structure, an adaptive shunt routing algorithm and a low-loss non-blocking 5-port optical router are designed, and an adaptive hybrid optoelectronic interconnection simulation model and performance statistical model based on System verilog and Verilog are established. The experimental results demonstrate that in the case of network edge node congestion, the routing algorithm designed to avoid congestion improves 17.5% on average, the number of cross waveguides and microring resonators required for optical routers is greatly reduced, and the average path insertion loss is only 0, 522 dB. The hybrid optoelectronic interconnection performance statistical model has function such as supporting the design of routing strategies and topology structures. It can perform statistics on resource usage, power consumption, insertion loss, and other performance.

**Key words:** optoelectronic hybrid interconnection on chip; electrical configuration router; shunt structure; optical router; performance analysis

## 1 引 言

随着集成电路工艺的快速发展,片上系统集

成核的数目越来越多,传统基于总线的互连结构难以适应复杂通信应用多样性的需求[1-3],数据传输和通信能力有限,易造成网络拥塞,进而影响处

收稿日期:2021-09-28 修订日期:2021-10-29

<sup>\*</sup> E-mail:jl@xupt.edu.cn

理器的性能。自适应光电混合互连网络能够兼顾光互连技术(optical network-on-chip, ONoC)和电互连技术的优缺点,分别为全局通信与局部通信提供光互连和电互连链路,成为新一代可重构阵列处理器簇间通信的一种有效解决方案。

国内外学者进行了大量地提高 HONoC(hybrid optoelectronic network-on-chip, HONoC) 自适 应能力的研究,JANG等[4]提出了一种由半导体 光放大器组成的低功耗可扩展的 HONoC 架构, 虽然有助于解决网络规模增大带来的插入损耗和 串扰噪声问题,但是激光器输出功率过大,网络性 能达不到人们的期望值。PARANE等[5]提出了 一种基于传统二级流水线实现的自适应、低成本 的路由器结构,它可以通过影响交叉开关、路由算 法和流水线优化的特性来保持路由器在大规模网 络工作负载下的性能。但引入旁路缓存和多路复 用器作为替代路径来容忍故障,增加了硬件开销 和功耗。KUMAR等[6]提出一种缓存深度可变的 自适应路由器结构,它可以将其它方向的缓存动 态分配给数据流量大的其它位置,虽然降低了该 自适应路由器的硬件开销和功耗,但总缓存深度 有限,缓存重配置耗时过长。NAIN[7]、LI[8]、 SHAFIEI 等[9]提出了一种适用于 Mesh 结构的自 适应容错路由算法,能够选择一个替代路径绕过 网络的拥塞区域,避免了活锁。但是,替代路径延 迟代价过高,网络划分方式复杂。该类方法虽然 都能够提高 HONoC 的自适应能力,但该类模型 都是基于现有的网络仿真平台[10-12]对性能进行测 试,无法实现光电联合仿真,不能对网络性能做出 准确的评判。

针对上述问题,本文提出一种适用于可重构阵列处理器的自适应光电混合互连分流结构,在此结构上设计了自适应分流路由算法与一种低损耗无阻塞的5端口光路由器,它可以根据网络拥塞情况动态地调整路由方向使网络负载分布均衡。此外为了更好地测试自适应光电混合互连分流网络的性能,本文搭建了基于 System verilog 与Verilog 的光电混合互连功能仿真与性能统计模型。实验结果表明,本文所设计的结构无论在网络性能还是资源占用量上都有较大的改善。

## 2 自适应光电混合互连分流网络结构

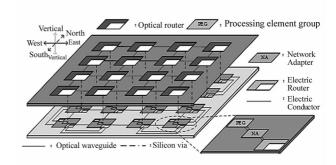

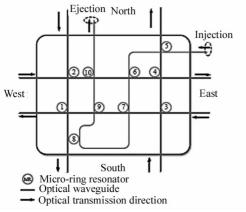

自适应光电混合互连分流网络整体结构如图 1 所示。底层为电网络层,它主要由轻核处理元簇 (processor element group, PEG)、网络适配器 (network adapter, NA) 与电路由器构成,上层为光网络层,由若干个 5 端口光路由器构成,层间通过硅通孔

协同电路由器来控制光链路的建立、响应和撤销,完成数据的正确通信。电路由器不仅需要完成数据的电路交换,还需要发送微环控制信号对光路由器进行配置,此结构在"电控制,光传输"思想的基础上,将电路由器外围路由节点中空闲的 I/O 端口进行连接,实现了边缘路由节点的数据分流。由于相邻处理元簇通信频繁,更容易造成网络拥塞,该分流结构解决了可重构阵列处理器由于网络拥塞导致性能下降的问题,即使通信模式是非均匀的,也能把网络负载均衡的分布到整个网络中去。

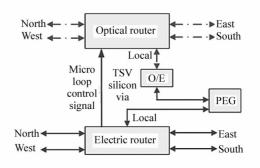

图 2 为光电结构协同工作示意图,当电路由器接收到来自处理元簇的访问请求信号,根据源节点、目的节点以及路由算法来建立路径,路径建立成功后,向源节点发送响应信号,同时根据路径选择来配置微环谐振器工作状态,让光网络层对应的光路由器处于数据传输状态,源节点接收到响应信号之后,将在光网络层根据设计的光路由器进行数据的传输。当数据接收完成之后,源节点给目的节点发送链路拆解信号,然后进行光链路的释放。光路由器的本地 IP 都要接入光电转换和电光转换单元,完成电信号和光信号之间的转换。

图 1 自适应光电混合互连分流网络整体结构

Fig. 1 Overall structure of adaptive photoelectric hybrid interconnection shunting network

图 2 光电结构协同工作示意图

Fig. 2 Schematic diagram of photoelectric structure cooperation

### 2.1 自适应可分流电路由器结构

电路由器不仅需要完成数据的电路交换,还需

要根据源节点与目的节点的位置进行链路建立、响应和撤销,在路径建立的同时配置微环谐振器的工作状态让数据无阻塞地到达目的节点。当路由器接收到建立包后,按照预定好的路由算法将数据从东、西、南、北或本地 IP 5 个方向传输到下级路由器,并且更新路由器的路径信息,更新包的输出端口号。链路建立完成后,目的节点产生响应包并且沿着链路建立成功的逆方向进行链路响应,源节点通过光网络层向目的节点进行数据分组传输,传输完成后,发出链路拆除请求,撤销包从目的节点沿着建立的链路回溯到源节点,根据包中记录的路径信息依次修改路由器中配置寄存器的值,达到撤销链路的目的。

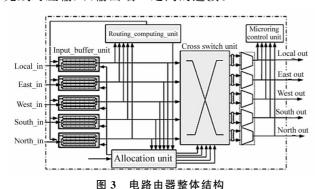

电路由器的整体结构和模块间连线如图 3 所示,由 5 个端口的输入缓存单元、路由计算单元、分配单元和交叉开关单元组成。输入缓存单元的功能是为了防止输入数据的阻塞和丢失,5 个方向进来的数据首先到达输入缓存,输入缓存包括本地(IP)输入、东向(E)输入、西向(W)输入、南向(S)输入和北向(N)输入 5 个模块,每个模块都有 4 深度的缓存空间。路由计算单元采用自适应分流路由算法,将数据按照路由算法计算出来的结果传输到下一级。分配单元对发起请求的端口进行仲裁,控制交叉开关的选择。交叉开关单元根据分配单元分配的结果,完成对应输入、输出端口之间的连接。

Fig. 3 Overall structure of electric router

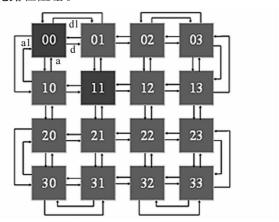

在 4×4 的 Mesh 网络中,边缘路由节点最外围的 I/O 端口是闲置的,为了更充分地利用片上网络中有限的通信资源,将电路由器外围路由节点中空闲的 I/O 端口进行连接,实现了边缘路由节点的数据分流。可分流电传输网络示意图如图 4 所示。以图 4 来说明增加路径 a1 和路径 d1 后数据传输方式的改变,从 Router00 来看,在增加路径 a1 后,从Router10 向 Router00 传输数据时可以使用 2 条路径 a 和 a1。在最坏情况下 3 个方向(Local\_IP、

North、East)的数据在同时向 Router00 路由时,路径 a 和 a1 可以同时响应其中 2 组数据的传输。同样地,在增加路径 d1 后,从 Router01 来看,从 Router00 向 Router01 传输数据时可以使用 2 条路径 d 和 d1。由此可以得出,新增的路径 a1 和路径 d1 起到了数据分流的效果,作为光电混合互连网络,光网路的加入更是丰富了路径的多样性,从 Router00 向 Router01 传输数据时不仅可以使用 2 条电传输路径 d 和 d1,而且还能使用 1 条光传输网络,同时可以将最坏情况下来自 3 个方向的数据同时传出,仅仅需要设计更合适的路由算法来对数据进行传输,就可以避免路径阻塞。

图 4 可分流电传输网络示意图 Fig. 4 Schematic diagram of shuntable

electric transmission network

## 2.2 低损耗无阻塞5端口光路由器结构

5端口光路由器用来实现不同节点之间的数据传输,它包含本地端口(Injection 和 Ejection)、北端口(North)、南端口(South)、西端口(West)和东端口(East)5个端口,它们由交叉开关及光波导组成。5端口光路由器结构如图 5 所示,同方向端口之间不进行数据通信,波导直接相连的 2 个端口之间不需要微环谐振器进行波长耦合,其余端口之间利用微环谐振器对光信号传输方向进行改变,从而使光信号传到固定的目的端口。其中微环谐振器 MR1、MR2、MR3、MR4、MR5 和 MR8 为多角度耦合微环谐振器,1个微环谐振器就可以实现 2 组端口之间的相互通信。

5端口光路由器仅使用 5条波导,10个微环谐振器就可以实现任意端口之间无阻塞通信。微环谐振器分配表如表 1所示,具体的通信过程如下,North端口不需要对North端口进行通信,North端口向South端口通过波导直接通信,不需要微环谐振器进行传输方向改变,当进行North端口到West

端口间通信时,信号从 North 端口输入,沿着波导传输,当传输到 MR1 时发生耦合,信号沿另一波导进行传输,到达 West 端口并输出。当 North 端口向East 端口通信时,信号从 North 端口输入,沿着波导传输,当传输到 MR2 时发生耦合,信号沿另一波导进行传输,到达 East 端口并输出。当 North 端口向Ejection 端口通信时,信号从 North 端口输入,沿着波导传输,当传输到 MR8 时发生耦合,信号沿另一波导进行传输,到达 Ejection 端口并输出。其余端口之间通信与 North 端口通信类似,同方向的端口之间不需要通信,波导连接的 2 个端口之间通过光波导之间进行数据通信,不需要经过微环谐振器,其余端口通过微环谐振器与波导的耦合,将数据传输到固定端口。

图 5 5 端口光路由器结构

Fig. 5 Structure of 5-port optical router

#### 表 1 微环谐振器分配表

Tab. 1 Distribution of microring resonator

| Out\In   | N_in | S_in | W_in | E_in | Injection |

|----------|------|------|------|------|-----------|

| N_out    | _    | NO   | MR4  | MR3  | MR5       |

| S_out    | NO   | _    | MR2  | MR1  | MR8       |

| W_out    | MR1  | MR3  | _    | NO   | MR7       |

| E_out    | MR2  | MR4  | NO   | _    | MR6       |

| Ejection | MR8  | MR5  | MR10 | MR9  | NO        |

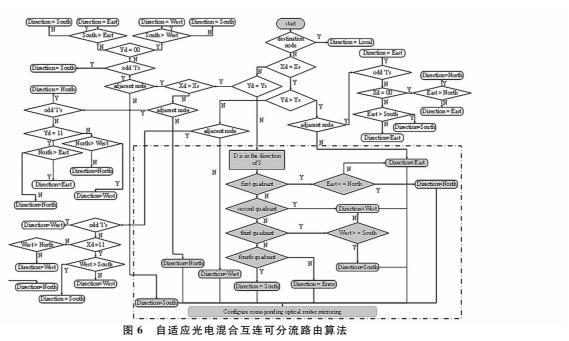

## 2.3 自适应光电混合互连分流路由算法

由于频繁的光/电转换会降低网络的工作性能, 电互连的功耗随其长度的增加而迅速增加,自适应 光电混合互连可分流路由算法(adaptive streaming routing algorithm, ASRA) 如图 6 所示,它可用于网 络内任意节点通信,相邻节点间通过片上电互连的 方式进行连接,使用电路交换进行通信,非相邻节点 通过片上光互连连接,通过光路由器进行通信。例 如 PEG00 发送数据给 PEG10, 一开始首先判断源节 点和目的节点 X 坐标是否相同,PEG00 的坐标为 4, b0000(X 坐标为 2'b00, Y 坐标为 2'b00), PEG10 的 坐标为 4'b0100, X 坐标不相同, Y 坐标相同, X 坐标 只相差 1,示为相邻节点,故选择电传输,随后分别判 断 2 节点位置情况,4'b0000 中'1'的个数为 0,4' b0100 中'1'的个数为 1,'1'的个数之和为 1,即为奇 数,源节点到目的节点间有2条路径可以选择,根据 西方向和南方向拥塞情况选择路由方向,如若南端 口拥塞情况大于西端口,则选择从增加的西端口分

Fig. 6 Adaptive routing algorithm for shuntable optoelectronic hybrid interconnection

流路径上输出,反之则从南端口输出数据。由于相邻簇间通信频率最高,易造成电网络拥塞,该自适应分流路由方式提供多种备选路径,避免了数据传到阻塞端口,从而提高处理器整体性能。

## 3 分析与讨论

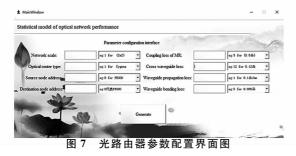

对于当前无法实现光电联合仿真,设计了自适应光电混合互连功能仿真和性能统计模型,分别用System verilog 和 Verilog 对光网络和电网络进行搭建,此仿真模型具有支持设计拓扑、结构(网络、路由器、链路和通道)、路由策略等功能,并可以对资源使用、功耗开销、插入损耗等基本性能进行统计。电路由器传出的数据通过 Interface 进行采集,使用Clocking 时钟块保证采样数据的正确性,光路由网络通过分析 Interfacec 采集的数据提取出源节点和目的节点,合理分配路由路径进行传输。

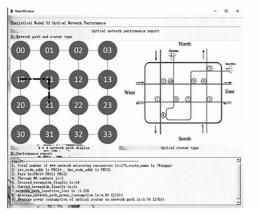

图 7 为光路由器参数配置界面图,它可以对网络规模、光路由器类型、微环谐振器耦合损耗、交叉波导损耗、波导传播损耗、波导弯曲损耗等参数进行配置。使用 Qt Creator 5.9 搭建图形化界面,生成配置参数保存到 config 配置文件中,使用 System verilog 读取 config 配置信息,并以此搭建光路由网络并使用 Questasim 10.4e 仿真器统计网络性能,将性能参数返回给图形化界面显示,光网络性能报告如图 8

Fig. 7 Optical router parameter configuration interface

图 8 光网络性能报告

Fig. 8 Optical network performance report

所示,图 8 左边为源节点到目的节点数据传输路径, 右边为网络中使用的光路由器,下面的报告对网络 资源使用、功耗开销、插入损耗等性能进行汇总 报告。

### 3.1 光电混合互连网络资源占用率分析

为了验证光电混合互连分流网络功能的正确性并统计硬件资源的开销情况,本文采用 Xilinx 公司的 VIVADO 开发环境进行下板测试,选用的器件是 Virtex UltraScale+系列 xcvu440 FPAG。表 2 和表 3 分别对图 1 所示的 4×4 光电混合路由网络的资源占用情况进行分析。数据表明,4×4 光电混合网络的时钟频率可以达到 227.560 MHz。电路由器查找表使用数量为 17 032 个,占板上资源的 0.67%,寄存器使用数量为 18 316 个,占板上资源的 0.36%。此外,由于目前的片上工艺还没有实现全光互连,本文使用 NE 公司生产的 NE-FMCH-SFP 光纤子卡,调用 Aurora 64B/66B IP 核对光路由器数据发送、接收端口的资源使用情况进行分析。光路由器接口端查找表使用数量为 72 048 个,占板上资源的 2.84%,寄存器使用数量为 123 624 个,占板上资源的 2.44%。

表 2 电网络逻辑资源占用分析

Tab. 2 Electrical network resource occupation

| Item    | 4×4 Electric router network |        |  |

|---------|-----------------------------|--------|--|

| Fre/MHz | 227.560                     | _      |  |

| LUT     | 17032/2532960               | 0.67%  |  |

| LUTRAM  | 309/459360                  | 0.07%  |  |

| FF      | 18316/5065920               | 0.36%  |  |

| BRAM    | 776/2520                    | 30.79% |  |

表 3 光网络逻辑资源占用分析

Tab. 3 Optical network resource occupation

| Item    | 5-port optical routing network |       |  |

|---------|--------------------------------|-------|--|

| Fre/MHz | 227.560                        | _     |  |

| LUT     | 72048/2532960                  | 2.84% |  |

| LUTRAM  | 7968/459360                    | 1.73% |  |

| FF      | 123624/5065920                 | 2.44% |  |

| BRAM    | 216/2520                       | 8.57% |  |

## 3.2 ASRA 算法路径建立周期分析

确定性路由算法(deterministic routing algorithm, DRA)在路径阻塞时,需要在路径拆解后才能

建立新的链路。为了验证 ASRA 路由算法的高效性,在边缘路径阻塞情况下(PEG00-PEG10、PEG02-PEG03、PEG23-PEG33、PEG 30-PEG31 4 条路径阻塞)对 2 种路由算法进行对比分析,表 4 统计了源节点 PEG00 到不同目的节点路径建立过程与微环配

置过程所需的时钟统计,结果表明,确定性路由算法 阻塞概率大,路径建立时间长,而 ASRA 算法可以通 过监测前方路径拥塞情况分流传输,相比确定性路 由算法避免拥塞能力平均提升了 17.5%,当端口阻 塞概率达到 80%时,才会导致路由器阻塞。

表 4 路径建立时间统计

Tab. 4 Statistics of path establishment time

| Src/Dst | DRA<br>Congestion | ASRA<br>Congestion | DRA<br>Build cycle | ASRA<br>Build cycle | Microring config-cycle |

|---------|-------------------|--------------------|--------------------|---------------------|------------------------|

| 00-01   | N                 | N                  | 3.5                | 3.5                 | -                      |

| 00-10   | Y                 | N                  | 7.5                | 4                   | =                      |

| 00-20   | Y                 | N                  | 9.5                | 7                   | 2                      |

| 00-22   | Y                 | N                  | 17                 | 9.5                 | 4                      |

| 00-33   | Y                 | N                  | 22.5               | 16.5                | 6.5                    |

### 3.3 5端口光路由器性能分析

对于光路由器而言,路由器所需的器件主要包括微环谐振器、光波导、弯曲波导、交叉波导和光终端。5端口光路由器利用多耦合微环谐振器开关,1条波导连接不同端口的输入和输出,不需要使用光终端,10个微环谐振器,9个交叉波导和5个弯曲波导就可实现任意端口之间的相互通信。表5为对不同5端口光路由器结构所需的器件数量进行统计。

结果表明,本文设计的光路由器相比于 Rigor<sup>[13]</sup>光路由器波导仅有 5 条,交叉波导数量减少 25%,弯曲波导数量减少 75%,微环谐振器数量减少 33.3%。相比于 Srax<sup>[14]</sup>光路由器,交叉波导数量减少 18.2%,弯曲波导数量减少54.5%,微环谐振器数量减少33.3%。相比于文献[15]虽然使用的微环谐振器增加了 2 个,但是,交叉波导数量减少 35.7%,弯曲波导数量减少 80.8%。

表 5 5 端口光路由器器件数量

Tab. 5 Number of five port optical router devices

| Router<br>structure          | Number of waveguides | Number of crossed/Bent<br>waveguides | Number of optical terminals | Number of microring resonators |

|------------------------------|----------------------|--------------------------------------|-----------------------------|--------------------------------|

| Rigor <sup>[13]</sup>        | 5                    | 12/20                                | 0                           | 15                             |

| $\operatorname{Srax}^{[14]}$ | 5                    | 11/11                                | 0                           | 15                             |

| $Surix^{[15]}$               | 5                    | 14/26                                | 0                           | 8                              |

| This paper                   | 5                    | 9/5                                  | 0                           | 10                             |

插入损耗大小主要由光路由器中的微环谐振器、交叉波导和弯曲波导的数量决定,不同文献插入损耗计算方法不同,所使用的损耗参数大小不一。 $L_{\text{insert}}$  为某一路径的插入损耗,在文献[16]与文献[13]中微环谐振器未发生耦合时的插入损耗值为0.005 dB,用 $L_{\text{through}}$ 表示。微环谐振器发生耦合时的插入损耗值为0.12 dB,用 $L_{\text{cross}}$ 表示。中于波导传播损耗、波导弯曲损耗较小,在分析插入损耗性能时忽略不计, $N_{\text{through}}$ 、 $N_{\text{drop}}$ 和 $N_{\text{cross}}$ 分别为该路径所经过的2种状态的微环谐振器数量和交叉波导数量。而在文献[14]中,将微环谐振器的损耗分为交叉开关损耗

和平行开关损耗,为了更公平的比较,用与文献保持 一致的公式计算光路由器上每条路径的插入损耗, 具体表达式为:

$$L_{ ext{insert}} = N_{ ext{through}} L_{ ext{through}} + N_{ ext{drop}} L_{ ext{drop}} + N_{ ext{cross}} .$$

(1)

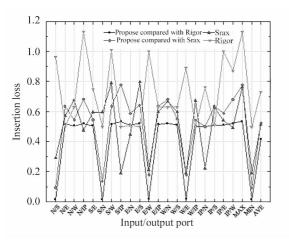

图 9 为不同 5 端口光路由器不同输入输出端口间的插入损耗,在此基础上求得路由器的最大、最小和平均插入损耗,其比较与评估如表 6 所示。可以分析出,所设计的光路由器在插入损耗上优于其他同类型路由器。与文献[16]、文献[13]的光路由器相比,平均插入损耗分别降低了 53. 4%、43. 2%,与文献[14]相比插入损耗虽然增加了 1.72%。但是减

少了33.3%的微环数目。

图 9 不同 5 端口光路由器插入损耗

Fig. 9 Insertion loss of different 5-port optical routers

表 6 插入损耗的比较与评估

Tab. 6 Comparison and evaluation of insertion loss

| Parameter | Ref. [16]<br>/This paper | Ref. [13]<br>/This paper | Ref. [14]<br>/This paper |

|-----------|--------------------------|--------------------------|--------------------------|

| Max. IL   | 1.260/0.535              | 1.130/0.535              | 0.765/0.775              |

| Min. IL   | 0.620/0.015              | 0.500/0.015              | 0.190/0.095              |

| Avg. IL   | 0.890/0.415              | 0.730/0.415              | 0.513/0.522              |

## 4 结 论

针对光电混合互连网络拥塞控制与自适应能力差、无法实现光电联合仿真等问题,结合可重构阵列处理器相邻处理元簇之间通信频繁的特点将电路由器外围闲置的 I/O 端口进行连接,得到一种适用于可重构阵列处理器的自适应光电混合互连分流结构,在此结构上设计了自适应分流路由算法与一种低损耗无阻塞的 5 端口光路由器,并搭建了基于System verilog 与 Verilog 的光电混合互连功能测试与性能统计模型,实验结果显示,电路由器工作频率高,抗阻塞能力强,光路由器资源开销小,插入损耗少,所设计的光电混合互连性能统计模型能够对混合光电 2 种传输模式的网络性能做出准确评判。

## 参考文献:

- [1] SU Y,XIE Y,SONG T,et al. A novel virtual-cluster based architecture of double-layer optical networks-on-chip[J].

IEEE Journal of Lightwave Technology, 2020, 38 (99): 1-

- [2] SHANG Y,GUO B,LI X,et al. Traffic pattern adaptive hybrid electrical and optical switching network for HPC sys-

- tem[J]. IEEE Communications Letters, 2019, 23(2); 270-273.

- [3] CHENG T, WU N, YAN G, et al. Poet; a power efficient hybrid optical NoC topology for heterogeneous CPU-GPU systems[C]//IECON 2019-45th Annual Conference of the IEEE Industrial Electronics Society, October 14-17, 2019, Lisbon, Portugal. New York; IEEE, 2019; 3091-3095.

- [4] JANG Y J, KIM M S, LI C L, et al. Power and signal-tonoise ratio optimization in mesh-based hybrid optical network-on-chip using semiconductor optical amplifiers[J]. Applied Sciences, 2019, 9(6):1251.

- [5] PARANE K, PRASAD B M P, TALAWAR B. Design of an adaptive and reliable network on chip router architecture using FPGA[C]//International Symposium on VLSI Design, Automation and Test, April 22-25, 2019, Hsinchu, Taiwan, China. New Tork; IEEE, 2019:1-4.

- [6] KUMAR D N P. Design of priority based reconfigurable router in network on chip[J]. Informacije Midem Ljubljana, 2019, 49(4): 203-210.

- [7] NAIN Z, ALI R, ANJUM S, et al. A network adaptive fault-tolerant routing algorithm for demanding latency and throughput applications of network-on-chip designs [J]. Eletronics, 2020, 9(7):1076.

- [8] LI J, CAI S, GUO R L, et al. A path-diversity routing algorithm with adaptive strategy for 3D network-on-chip[J]. Microeletronics & Computer, 2019, 36(2): 46-52. 李娇, 蔡升, 郭润龙, 等. 一种具有路径多样性的自适应 3DNoC 路由算法[J]. 微电子学与计算机, 2019, 36(2): 46-52.

- [9] SHAFIEI F, SATTARI V. Development of an adaptive multipath routing algorithm by examining the congestion and channel fault of one-hop nodes in network-on-chip[C]//8th International Conference on Computer and Knowledge Engineering, October 25-26, 2018, Mashhad, Iran. New Tork: IEEE, 2018: 231-236.

- [10] SADAGHIANI A V K, GHANBARI M. An optimized hardware design for high speed 2D-DCT processor based on modified Loeffler architecture[C]// 2019 27th Iranian Conference on Electrical Engineering (ICEE), April 30-May 2, 2019, Yazd, Iran. New Tork: IEEE, 2019: 1476-1480.

- [11] ZHANG J F,SHI W,ZHOU L,et al. A low-power and highpsnr unified DCT/IDCT architecture based on EARC and enhanced scale factor approximation[J]. IEEE Access,

- 2019,99(7):165684-165691.

- [12] BISWAS A K. Efficient timing channel protection for hybrid (packet/circuit-switched) network-on-chip[J]. IEEE Transactions on Parallel and Distributed Systems, 2018, 29(99):1044-1057.

- [13] YAHYA M R, WU N, FANG Z, et al. A low insertion loss 5 ×5 optical router for mesh photonic network-on-chip to-pology[C]//2019 IEEE Conference on Sustainable Utilization and Development in Engineering and Technologies (CSUDET), November 7-9, 2019, Penang, Malaysia. New Tork; IEEE, 2019; 164-169.

- [14] SHI X,WU N,GE F,et al. Srax: a low crosstalk and insertion loss  $5\times 5$  optical router for optical network-on-chip  $[\mathbf{C}]//45$ th Annual Conference of the IEEE Industrial Electronics Society, October, 14-17, 2019, Lisbon, Portugal.

New Tork: IEEE, 2019: 3102-3105.

- [15] ASADINIA S, MEHRABI M, YAGHOUBI E. Surix: non-blocking and low insertion loss micro-ring resonator-based optical router for photonic network on chip[J]. The Journal of Supercomputing, 2020, 77(5): 4438-4460.

- [16] SELVIAH D R,YU Z H,Microring resonator-based optical router for photonic networks-on-chip[J]. Quantum Electronics, 2016, 46(7):655-660.

#### 作者简介:

**蒋** 林 (1970-),男,博士,教授,博士生导师,主要从事专用集成 电路与高性能计算机方面的研究.